ATB协议

ATB协议

Tim Dong介绍

ATB 协议属于 AMBA 协议的一部分

ATB v1.0是AMBA 3的一部分ATB v2.0是AMBA 4的一部分ATB-C是AMBA 5的一部分

ATB 协议定义了 Trace 信息如何在跟踪系统中的组件之间传输。ATB 是跟踪组件用来通过 CoreSight 系统传递格式独立的跟踪数据的通用总线。

具有跟踪功能的跟踪组件或平台需要 ATB 接口。ATB 接口由以下任一方式指定:

- 发送器 在

ATB总线上生成跟踪数据的接口。 - 接收器 从

ATB总线接收跟踪数据的接口。

ATB 接口支持各种功能,包括:

- 使用

valid和ready响应来停止数据。 - 控制信号,指示一个周期内有效的字节数。

- 通过发送与每个数据包相关的

ID来识别原始组件。 - 支持任何跟踪协议信息、数据信息或数据格式要求。

Flushing。

接口

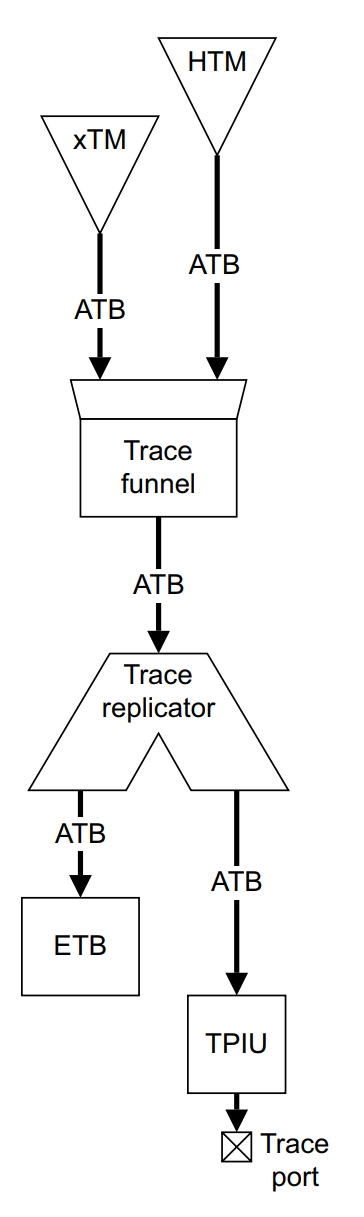

ATB 是跟踪组件使用的通用总线,用于以数据不可知的格式在系统中传递跟踪数据。ATB 协议定义了总线行为,接口信号根据其功能命名。ATB 与关联组件的一般关系如图所示:

| 简称 | 全称 | 描述 |

|---|---|---|

HTM |

Advanced High-performance bus Trace Macrocell |

这将输出描述其正在监控的 AHB 互连相关的跟踪信息。 |

ETM |

The Embedded Trace Macrocell |

ETM 可以生成指令跟踪,也可以生成数据跟踪。 |

PTM |

The Program-flow Trace Macrocell |

PTM生成指令跟踪。 |

ETB |

Embedded Trace Buffer |

这是片上跟踪数据存储设备。 |

TPIU |

Trace Port Interface Unit |

这是一个将 ATB 连接到跟踪端口以提供跟踪数据的外部存储的设备。 |

Trace funnel |

这将多个跟踪源合并到单个总线上。 | |

Trace replicator |

这会将单个 ATB 接收器接口复制到两个独立的 ATB 发射器。 |

Trace 系统包括:

- 至少一个跟踪数据源,例如

ETM或HTM - 至少有一个跟踪数据接收器或接收者,例如

ETB或TPIU

在跟踪源和接收器之间,可以存在Trace Link来帮助管理通过ATB接口传输数据,例如Trace Funnel和Trace replicator。

跟踪源生成ATB数据流量,这些数据流量可由ATB路径上的Trace Link管理。Trace Link可将信息重新传输到Trace Sinks。Trace Sinks充当跟踪源生成的跟踪数据的接收器。

通常,Trace Sink可以请求刷新跟踪结构,以确保已收到特定时间之前的所有跟踪数据。这些刷新请求会从Trace Sinks向跟踪源传播回ATB系统。在收到刷新请求后,跟踪源会标记刷新请求之前发生的所有数据,并在输出所有这些数据后指示完成。ATB系统中的任何Trace Link都必须: - 将刷新请求传递至其连接的跟踪源。

- 确保只有在所有连接的跟踪源都确认完成后才确认刷新完成。

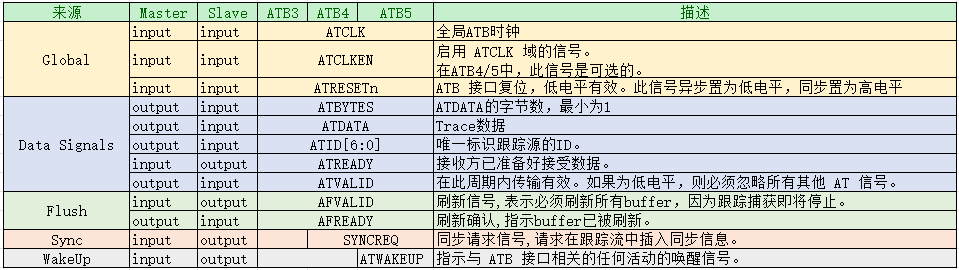

信号描述

数据流控制

ATB 数据流控制机制是一种双向流控制,发送器和接收器可以使用它来控制数据和控制信息的移动速率。Master 生成 ATVALID 信号以指示数据或控制信息何时可用。Slave 生成 ATREADY 信号以指示它接受数据或控制信息。

仅当 ATVALID 和 ATREADY 信号都为高电平时才会传输数据。

ATVALID 和 ATREADY 在发送器和接收器之间提供握手,以指示跟踪数据项的可用性:

- 发送器通过断言

ATVALID来指示它有可用于输出的跟踪。 - 如果接收器可以接受跟踪数据,它会通过拉高

ATREADY来响应。如果接收器无法接受跟踪数据,或者没有拉高ATREADY信号,则必须在下一个周期再次输出相同的跟踪。

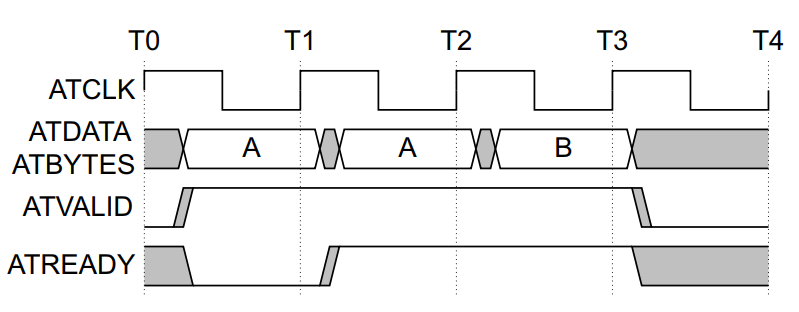

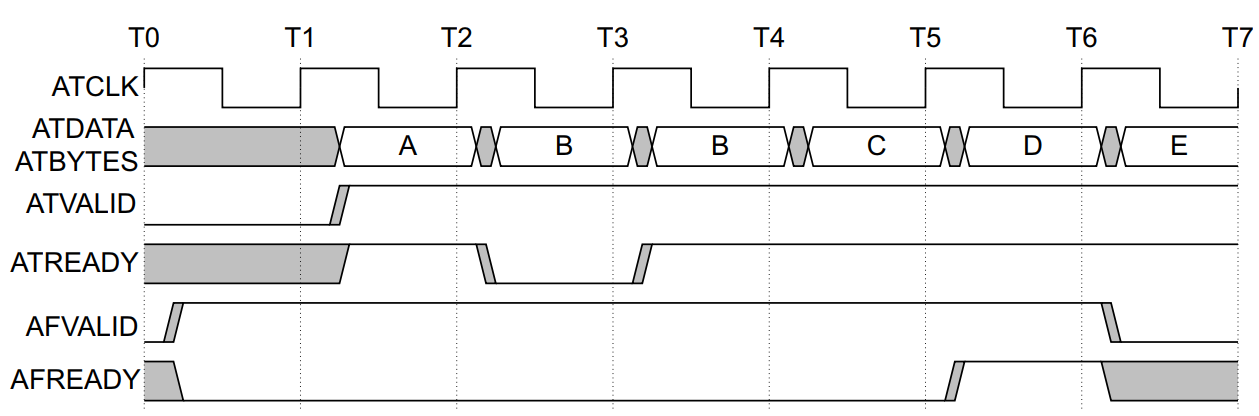

数据流控制波形

- 仅当

ATRESETn在ATCLK的上升沿变为高电平后,跟踪源才可以开始驱动ATVALID为高电平。 - 尽管

ATRESETn可以异步置为低电平,但置低必须与ATCLK的上升沿同步。 - 如果在某个周期内

ATREADY为低电平且ATVALID为高电平,则ATVALID、ATDATA、ATID和ATBYTES必须在下一个周期保持相同的值。 - 如果

ATVALID为低电平,则必须忽略ATREADY。

| 时钟周期 | 状态 |

|---|---|

T1 |

跟踪停止,ATREADY 未拉高 |

T2 |

数据A被采用 |

T3 |

数据B被采用 |

T4 |

跟踪被忽略,无 valid |

如果接收器的实现不能保证在 ATVALID 被拉高的同一周期内用 ATREADY 做出响应,则建议接收器实现足够的内部缓冲。此内部缓冲必须足以存储一个或多个跟踪周期。然后,当缓冲区中有可用空间时,接收器可以拉高 ATREADY,即使未拉高 ATVALID。

ATDATA 和 ATBYTES 之间的关系

以下公式定义了 ATBYTES 和 ATDATA 的宽度之间的关系,由 ATBYTES[m: 0] 和 ATDATA[n: 0] 中的 m 和 n 的值定义:

$$m = log_2(n+1) - 4$$

使用此公式,下表显示了 ATBYTES[m: 0] 和 ATDATA[n: 0] 之间的关系。

ATDATA[n: 0] |

ATBYTES[m: 0] |

|---|---|

n = 7 |

不需要 ATBYTES |

n = 15 |

m = 0 |

n = 31 |

m = 1 |

n = 63 |

m = 2 |

n = 127 |

m = 3 |

例如,如果 ATDATA 为 32 位宽(n=31),则 ATBYTES 为 2 位宽(m=1)。如果 ATREADY 和 ATVALID 均为高电平,则必须捕获 ATDATA 的底部字节,并且数据必须与最低有效位对齐。 |

📢 注意:

- 无法捕获零字节。

ATDATA的宽度必须是2的幂,且等于或大于8位。

接收方无法响应

如果接收器接口无法响应,它必须将 ATREADY 驱动为高电平并将 AFVALID 驱动为低电平。

📢 注意:

- 这确保了复制器不会因为其两个输出之一被禁用而阻塞。

接收器无法响应的示例包括:

- 接收器断电。

- 接收器不存在。

- 系统编程错误。

发射方无法响应

如果发送器接口无法响应,则必须将 AFREADY 驱动为高电平并将 ATVALID 驱动为低电平。

发送器无法响应的示例包括:

- 发送器断电。

- 发送器不存在。

- 系统编程错误。

其他 ATB 功能

ATIDs

跟踪数据项使用单独的 ID 生成。

这些单独的 ID 可以提供:

- 区分来自不同来源的跟踪。

- 识别跟踪的高带宽和低带宽组件,以便跟踪源下游的组件可以执行选择性过滤。

- 通过在对齐同步点(例如跟踪数据包的开头)更改

ID来对齐同步信息。

大多数源使用单个静态ID。

ATB 跟踪数据项可以使用

0x01-0x6F范围内的任何ATID值- 从

ATB-B(v 1.1)及更高版本,ATID值0x7D,但只能生成跟踪触发器。

📢 注意:

ATID值0x00、0x70-0x7C、0x7E和0x7F保留供CoreSight架构使用,不得用作ATB IDs。

有两个选项可以确保不同的跟踪流使用唯一的 ID 值:

- 固定IDs: 所有

ATB接口源的ID都是在设计系统时选择的,并且不会从系统中导出任何ATB接口。 - 程序IDs: 每个

ATB接口源的ID均可由调试器进行编程,从而允许在更大的系统中重复使用组件。可重复使用的CoreSight组件必须实现已编程的ID。

实现必须确保在捕获ATID上的字节的同时捕获ATDATA值。

Trace 字节顺序

ATB 实现必须保留跟踪字节的顺序,即使在具有不同 ATID 的跟踪之间也是如此。尽管 CoreSight Trace Funnel 可以按任意顺序对来自不同源的跟踪进行排序,但当漏斗到单个总线上时,顺序不能更改。

📢 注意:

- 这与

AXI接口中按ID信号要求的排序不同,AXI接口中仅在具有相同ID的事务之间保留排序。

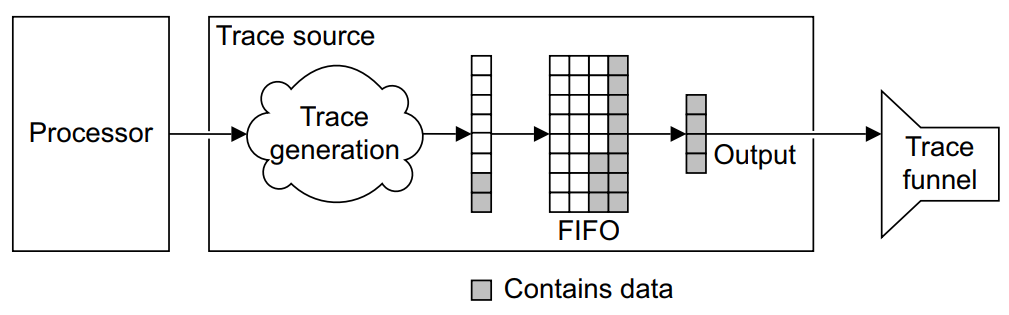

Buffer Flushing

跟踪数据项缓冲的特性意味着,随着周期的进展,通常需要从缓冲区中删除剩余数据以准备新数据。从缓冲区中删除数据的过程称为刷新。

在典型的跟踪源中,在要跟踪的事件发生和该事件的跟踪生成之间存在固定的时间量和流水线阶段数。处理器执行的指令就是一个例子。

生成跟踪数据项时,会将其写入 FIFO。数据从 FIFO 输出,每次输出一个完整的数据字。ATDATA 总线的宽度定义了数据字的大小。

理论上,跟踪生成和输出之间的时间间隔是无限的,因为 FIFO 可能永远不会收到足够的跟踪数据来填充整个输出数据字。生成和输出之间可能延长延迟的一个例子是,跟踪源会保留输出,直到它有整个跟踪数据字可供输出。

在仅当整个数据字可用时才输出数据的系统中,有多种情况可能需要刷新缓冲区。例如:

系统或系统的一部分即将断电或时钟即将停止。在断电或停止时钟之前,必须输出跟踪源中缓冲区或

FIFO内剩余的任何跟踪。因此,AFVALID信号发出刷新信号。通常,在发出刷新信号后,不会再生成跟踪,因为处理器和内存活动已停止。如果在刷新后生成跟踪,则可以忽略它。刷新后生成的跟踪数据的一个例子是来自处理器空闲循环的数据。跟踪捕获设备即将停止捕获,通常是由于触发点。跟踪捕获设备可能是片外跟踪端口分析器 (TPA) 或片上嵌入式跟踪缓冲器 (ETB)。在这种情况下,可能包括:

- 向片上逻辑发出信号,表示捕获即将停止。此时会发出刷新指令。

- 片上逻辑会收到有关触发器的信号,但不会收到有关要捕获多少额外跟踪的任何信息。可以在触发点发出刷新。这可确保捕获触发器之前生成的所有跟踪,但对触发器之后生成的跟踪没有影响。

- 刷新是定期发出的。必须选择为刷新定义的周期,以便刷新始终发生在触发发生和跟踪捕获停止之间。当刷新发生时(由

AFVALIDHIGH指示),协议期望trace funnel为尚未拉高AFREADY的跟踪源提供最高优先级。

📢 注意:

- 刷新序列启动后,接收器接口无法取消该序列。这意味着,跟踪接收器无法取消该序列。

- 实现时必须确保在

ATCLK的上升沿对ATB信号进行采样。AFVALID信号保持有效,直到AFREADY被取消有效。

当 AFVALID 置位时生成的所有跟踪都已输出时,AFREADY 置位。AFREADY 置位并不表示 FIFO 为空。

在 AFVALID 置位后生成的跟踪存储在 FIFO 中。然后在 AFREADY 置位后输出此跟踪。

当 AFVALID 置位时,发送器必须立即开始输出缓冲跟踪。当发送器置位 AFREADY 时,如果不需要额外刷新,接收器必须在下一个周期取消置位 AFVALID。

当 AFVALID 置位时,发送器必须在输出在 AFVALID 首次置位的周期中缓冲的数据后一个周期置位 AFREADY。也就是说,它必须在输出 AFVALID 置位要求其刷新的最后一个数据后一个周期置位 AFREADY。

| 时钟周期 | 状态 |

|---|---|

T1-T2 |

已请求刷新。值 A、B 和 C 保存在 FIFO 中。 |

T2 |

开始 Flushing |

T3-T5 |

仍有可能出现 Stalls |

T6 |

Flush 完成。输出继续。 |

T6 |

AFVALID 拉低 |

不在本地存储跟踪的跟踪源的行为

如果发射器接口是一个不存储任何本地跟踪的跟踪源,下表显示了它如何控制 AFREADY。

ATVALID |

ATREADY |

AFREADY next cycle |

|---|---|---|

0 |

- |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

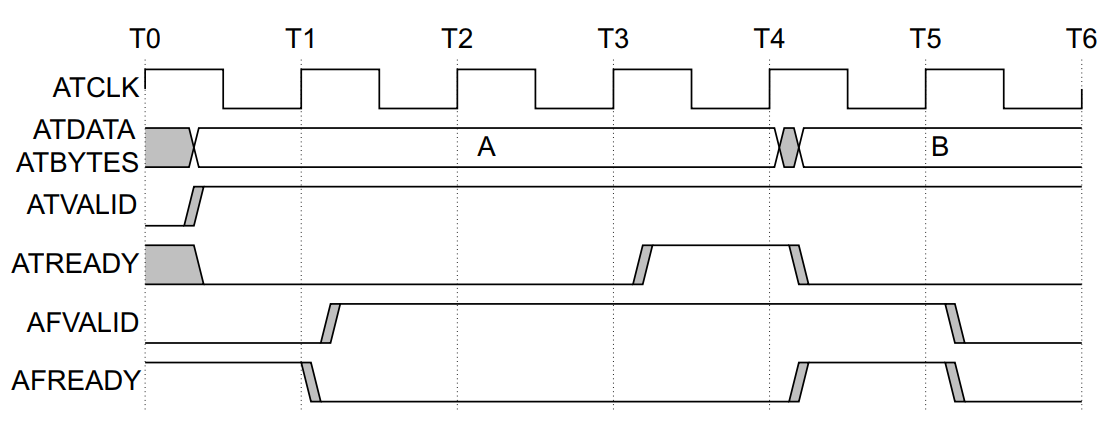

下图显示了没有在本地存储任何跟踪的发送器的AFREADY控制:

| 时钟周期 | 状态 |

|---|---|

T1 |

发送端生成数值A |

T2 |

Flush请求,值 A 现在是旧数据 |

T3 |

Flush 未完成,因为旧值 A 仍存在于发送端中 |

T4 |

值 A 被接收端接收 |

T5-T6 |

发送端中生成新值 B,Flush 请求被确认 |

Trace Trigger

Trace Trigger 信号是从跟踪源到跟踪接收器的实现定义消息。通常,它可能用于指示已发生重大情况并且跟踪捕获应准备停止。在 ATB Issue B 中,发送器可以按如下方式发出 Trace Trigger 信号:

ATID值必须为0x7D。ATBYTES表示此周期输出的跟踪触发器数。建议尽可能一次只生成一个Trace Trigger。在这种情况下:- 只有一个字节的数据。

ATBYTES为零。

ATDATA指示每个信号Trace Trigger的来源,如下所示:- 每个数据字节指示一个单独的

Trace Trigger - 为零的数据字节指示来自未知来源的触发器。建议跟踪源不要使用此值。

- 非零的数据字节指示生成

Trace Trigger的跟踪源的 ID。

例如:

- 每个数据字节指示一个单独的

使用

ATID0x10作为ATB信号的跟踪源可以通过生成一个跟踪数据字节来指示其ATB接口上的触发器:ATID信号0x7D,指示跟踪触发器。ATBYTES信号0x0,指示单个数据字节。ATDATA信号0x10,指示跟踪源 ID。

使用

ATID0x10和0x12的跟踪流可以通过生成两个字节的跟踪数据来指示两个跟踪源上的同时跟踪触发:ATID信号0x7D,指示跟踪触发。ATBYTES信号0x1,指示两个数据字节。ATDATA信号0x1210,指示跟踪源 ID 为0x10和0x12。

同步请求

ATB4 实现可以选择性的包括 SYNCREQ 同步请求信号。接收器(Slave)通过将 SYNCREQ 置为高电平持续一个 ATCLK 周期来向发送器发出同步请求信号。或者,发送器(Master)可以实现 SYNCREQ 输入。当此输入置为高电平持续一个 ATCLK 周期时,发送器可以识别来自接收器的同步请求。SYNCREQ 信号与 ATB 接口上的任何其他信号都没有任何关系。但是,从 ATB-B (v 1.1) 开始,规范要求:

SYNCREQ与其他 ATB 信号一起通过系统路由。- 任何

Trace Link(例如Trace Funnel)将输入同步请求从ATB发送器接口传递到上游跟踪源。

启用的跟踪源必须尝试为收到的每个同步请求在跟踪流中提供一次同步信息。跟踪源可以: - 延迟输出同步信息以避免溢出任何内部缓冲区。

- 忽略在跟踪源输出与上一个同步请求相对应的同步信息之前收到的同步请求。

ATB发送器必须知道可能随时收到SYNCREQ上的脉冲,并且必须确保它在需要时响应SYNCREQ。

接口信号规则

ATB 协议信号必须符合以下规则:

- 必须在

ATCLK的上升沿采样 ATB 信号。 - 如果在某个周期内

ATREADY为低电平且ATVALID为高电平,则ATVALID、ATDATA、ATID 和ATBYTES必须在下一个周期保持相同的值。如果ATVALID为低电平,则必须忽略ATREADY。 - 如果

ATREADY和ATVALID为高电平,则必须捕获ATDATA的底部字节。数据必须与最低有效字节对齐。

📢 注意:

无法采样零字节。 ATDATA的宽度(以位为单位)必须是2的幂,且大于或等于8。ATBYTES[m: 0]和ATDATA[n: 0]的宽度之间的关系由以下公式定义:$$m = log_2(n+1) - 4$$- 必须同时获取

ATID和ATDATA的值。 - 必须保留跟踪字节的顺序,即使在具有不同

ATID的跟踪之间也是如此。CoreSightTrace Funnel可以按任意顺序对来自不同源的跟踪进行排序。当Funnel到单个总线上时,顺序不能更改。

📢 注意:

这与AXI接口所需的顺序不同,其中仅在具有相同ID的事务之间保留顺序。 - 当

AFVALID被置位时,它必须保持置位状态,直到AFREADY被置位。当AFVALID被置位时,AFREADY将被忽略。 - 当

AFVALID被置位时,发送器必须立即输出任何缓存的踪迹。 - 当

AFREADY被置位时,除非需要额外刷新,否则AFVALID必须在下一个周期被置位。 - 当

AFVALID被置位时,发送器必须在输出其生成和存储的最后一个踪迹(直到并包括在AFVALID被置位的周期中生成的任何踪迹)后一个周期置位AFREADY。 ATRESETn可以异步置位。但是,ATRESETn必须在ATCLK的上升沿同步释放。

📢 注意:ATRESETn是低电平有效信号,这意味着它必须被置为低电平。- 仅当

ATRESETn在ATCLK的上升沿变为高电平后,跟踪源才可以开始驱动ATVALID为高电平。 - 每当

接收器接口无法响应时,必须将ATREADY驱动为高电平,并将AFVALID驱动为低电平。这种情况必须发生的情况包括断电、接收器不存在以及系统编程不正确。这可确保复制器不会因为其两个输出之一被禁用而阻塞。 - 每当

发送器接口无法响应时,AFREADY必须驱动为高电平,ATVALID必须驱动为低电平。这种情况必须发生的示例包括断电、发送器不存在以及系统编程不正确的结果。 ATID、ATBYTES和ATDATA可以具有任何值。此允许行为可用于绑定未使用的CoreSightTrace Funnel输入信号。ATID值0x00、0x70-0x7C、0x7E和0x7F保留供CoreSight架构使用,不得用作ATB ID。

Wake-Up 信号

Wake-Up 信号用于指示与 ATB 接口相关的活动。这可用于提供glitch-free信号,该信号可路由到时钟控制器或类似组件,以启用所连接组件的电源和时钟。Wakeup_Signal 属性用于指示组件是否支持唤醒信号:

True唤醒信号存在。False唤醒信号不存在。

如果未声明Wakeup_Signal,则视为False。唤醒信号只能添加到ATB5接口。

| 信号 | 位宽 | 源 | 描述 |

|---|---|---|---|

ATWAKEUP |

1 |

Master |

唤醒信号。表示存在与 ATB 接口相关的活动。 |

ATWAKEUP 的规则如下:

ATWAKEUP与ATCLK同步,但更适合跨时钟域连接到控制器。ATWAKEUP必须是glitch-free并直接从寄存器生成。- 允许在

ATVALID拉高之前或之后的任何时间点拉高ATWAKEUP。 - 允许接收器等待

ATWAKEUP拉高,然后再拉高ATREADY。这意味着如果ATWAKEUP存在但从未拉高,ATB接口可能会死锁。 - 如果

ATWAKEUP和ATVALID在同一周期内为高电平,则ATWAKEUP必须保持高电平,直到拉高ATREADY。

建议: - 在

ATVALID拉高之前至少一个周期拉高 ATWAKEUP,以防止延迟接受新事务。 - 当不需要进一步传输时,

ATWAKEUP拉低。允许但不建议在未发生事务的情况下拉高ATWAKEUP然后拉低。